EvolVerilog (Spring 2012)

Can computer design themselves? A team of four used evolutionary algorithms in Python to generate Verilog hardware implementations of systems. Our code is available on github. We presented our results at the CCSCNE 2012 and took first place in the Undergraduate Research Competition.

The GoalThe design of computer architecture is an incredibly challenging, time-consuming and necessarily human endeavor. We wish to create an alternative method by which computers self-organize to perform tasks efficiently, even when the ideal hardware implementation is not known to the designer.

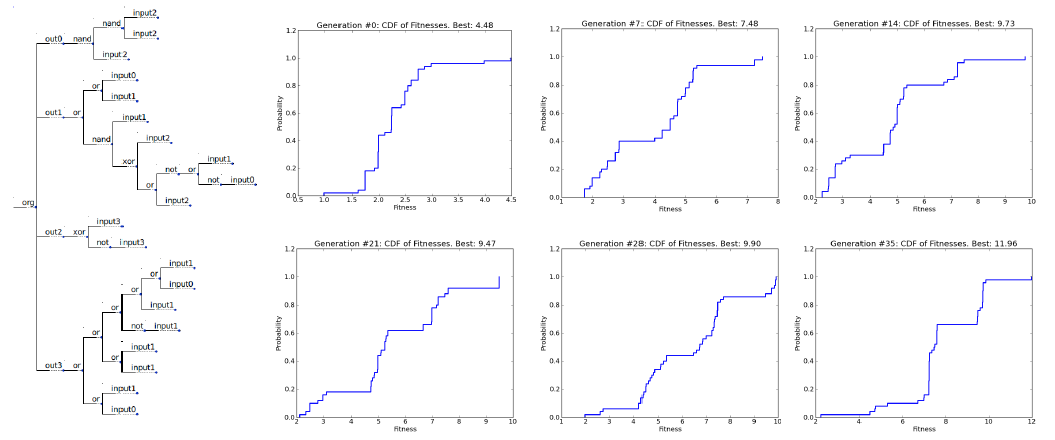

The ProcessDrawing inspiration from the field of artificial intelligence, we decided to apply a genetic algorithm to the problem of hardware design. A genetic algorithm works similarly to natural evolution, combining good traits from a population of organisms (solutions) over time through selective reproduction based on fitness, mutation, and genetic exchanges.

|

The SolutionWe chose to represent the hardware organisms in Verilog, a hardware description language, allowing us to test hardware performance virtually. The evolution was directed by a Python program which generated the Verilog hardware descriptions. Preliminary results show that this technique can develop unique and creative solutions to problems, even when a solution is not known a priori. For more detail, see our poster.

My Responsibilities

|